企業リリース Powered by PR TIMES

PR TIMESが提供するプレスリリースをそのまま掲載しています。内容に関する質問 は直接発表元にお問い合わせください。また、リリースの掲載については、PR TIMESまでお問い合わせください。

(2024/10/17)

カテゴリ:商品サービス

リリース発行企業:OKI

ヘテロジニアス集積に応用可能な「薄膜チップレット技術」の開発

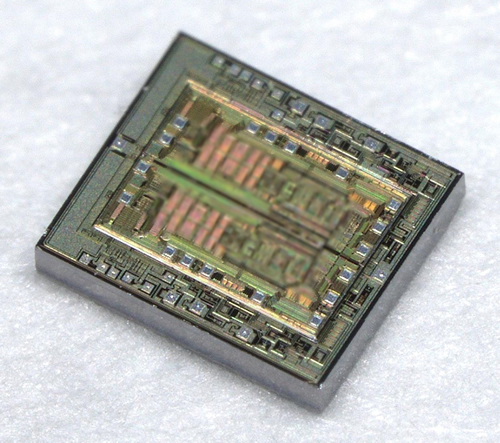

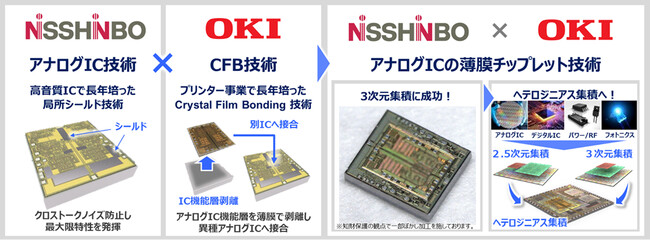

OKIは、日清紡マイクロデバイス株式会社(東京都、代表取締役社長 吉岡 圭一)と共同で、CFB(R)(Crystal Film Bonding)技術(注1)を用いて薄膜アナログIC(注2)の3次元集積(注3)に成功しました。本技術は、アナログICなどの多様な半導体デバイスを集積するヘテロジニアス集積(注4)に応用可能です。両社は本技術を用いた製品開発を進め、2026年の量産化を目指します。

近年、AI、自動運転の普及に伴い、半導体デバイスのさらなる高機能化のニーズが高まる中、チップレット技術(注5)が注目されています。チップレット技術は、全機能を単一チップへ集積するのでなく、機能ごとに小片チップに分割し、2.5次元・3次元の実装技術で統合することで、大規模な機能集積を低コスト・省面積で実現します。また、分割することで歩留りを向上し、各機能を実現するための最適な半導体製造プロセスを選択できるため、コスト増大を抑制します。

従来のチップレット技術をローエンドなアナログICの3次元集積に適用するためには、主に以下の2つの課題がありました。

1つ目の課題は、レガシープロセス(注6)で対応可能な3次元集積技術の開発です。3次元集積は、チップを垂直に積層するため集積度向上や小型化に大きく貢献します。しかし、積層するチップ同士の電気的な接合には、一般にTSV(Through Silicon Via)技術(注7)が用いられるため、設備投資や高度なプロセス開発が必要です。このため、従来の技術では高価なプロセスとなります。

2つ目の課題は、電気信号の干渉によるノイズ(クロストークノイズ)の防止です。アナログICは、「0」と「1」だけでなく連続的な信号変化全体に意味を持ち、デジタルICと比較して高い電圧の信号を取り扱います。そのため、積層によりICの回路層が近接すると、クロストークノイズが増大します。

OKIは、1つ目の課題を解決するために、新たに「薄膜チップレット技術」を開発しました。本技術は、剥離・接合のCFBプロセスと、その後の再配線で構成されます。まず、アナログICの機能を完全に保護し、アナログICの機能層のみを基板から剥離します。この薄膜アナログICを異なるアナログIC上に接合することで、薄膜アナログICの3次元集積に成功しました。一般的なTSVによる3次元集積の場合、ICチップの厚みは数十~数百µmですが、本技術により接合された薄膜アナログICの厚みは数µmと極めて薄いため、一般的な半導体リソグラフィ(注8)による再配線が可能です。本技術による再配線は、一般的で安価なレガシープロセスの適用が可能になります。

2つ目の課題を解決するために、日清紡マイクロデバイス株式会社独自の局所シールド技術をアナログICに適用しました。この技術は、チップ全体ではなく、上下チップ間で影響がおよぶ特定の箇所にのみシールドを施すことで、回路機能を低下させることなく信号干渉を抑える技術です。今回、同社は高音質ICで長年培ったローノイズアナログIC技術を活かすことで本技術を開発し、20Vppの高い電圧出力下においても、クロストークノイズの抑制をすることで正常な動作検証に成功しました。

日清紡マイクロデバイス株式会社とOKIの共創よる薄膜アナログICの3次元集積の成功は、さまざまなアナログICとの組合せによるアナログソリューションの提供を可能にします。また、OKIの「薄膜チップレット技術」をデジタル・アナログ・光・パワー・センサーなど、さまざまな半導体デバイスのヘテロジニアス集積に応用することで、半導体デバイスの新たな進化に貢献します。

今後、両社は、本技術による新たな付加価値をもつ製品の開発を進め、パートナーリングやライセンシングも視野に2026年の量産化を目指します。

なお、本技術について2024年10月23日~24日にベルサール東京日本橋で開催される「OKI WORLD 2024(https://www.oki.com/jp/ad/ow2024/#seminar)」にて、デモ展示を行います。また、同展示会のセミナーで詳細な説明を行います。

用語解説

注1:CFB(Crystal Film Bonding)技術

半導体デバイス機能層を薄膜剥離し、異なる材料基板に分子間力で接合するOKIの独自技術。接着剤を介さない直接接合のため、接合間で電気・光・熱など伝搬でき、接合後の半導体プロセスが可能なため、異種材料・機能を統合した新たな半導体デバイスの創出に貢献する。

注2:アナログIC

センサーなどの連続的に変化するアナログ信号を増幅・フィルタリング変換などを行う処理機能を有する集積回路(Integrated Circuit)。

注3:3次元集積

半導体デバイスを垂直方向に積層し、階層間で電気的接続を行う技術。

注4:ヘテロジニアス集積

異なるプロセスノード(微細加工技術の世代)、異なる機能(デジタルIC、アナログIC)、異なる半導体材料(光デバイス、次世代半導体)など、異なる半導体デバイスを複合的に組合せて集積する技術。

注5:チップレット技術

単一チップの半導体デバイスを、複数の小片チップ(チップレット)に分割し、実装技術で集積する技術。これにより、高機能化による大規模化における歩留まりの改善が可能。

注6:レガシープロセス

旧世代の製造技術や設備を用いた半導体製造方法。安定性や信頼性に優れ、コスト効率が高いため現在も多くの半導体プロセスで使用されている。

注7:TSV(Trough Silicon Via)技術

シリコン基板に垂直な貫通電極を形成することで、垂直方向の半導体チップ間の電気接続を実現する技術。

注8:半導体リソグラフィ

半導体プロセスにおいて、光や電子ビームを使用して半導体基板上に極めて微細な回路パターンを形成する技術。

リリース関連リンク

日清紡マイクロデバイス株式会社プレスリリース

https://www.nisshinbo-microdevices.co.jp/ja/about/info/20241017.html

OKI WORLD 2024(セミナー「S-1」10月23日11時10分~11時50分)

https://www.oki.com/jp/ad/ow2024/#seminar

沖電気工業株式会社は通称をOKIとします。

CFBは、沖電気工業株式会社の登録商標です。

その他、本文に記載されている会社名、商品名は一般に各社の商標または登録商標です。

本件に関する報道機関からのお問い合わせ先

広報室

お問い合わせフォーム

https://www.oki.com/cgi-bin/inquiryForm.cgi?p=015j

本件に関するお客様からのお問い合わせ先

グローバルマーケティングセンター CFB開発部

お問い合わせフォーム

https://www.oki.com/cgi-bin/inquiryForm.cgi?p=107j

企業プレスリリース詳細へ

PRTIMESトップへ

※ ニュースリリースに記載された製品の価格、仕様、サービス内容などは発表日現在のものです。その後予告なしに変更されることがありますので、あらかじめご了承下さい。